Holes are repelled-leaving behind a carrier depletion-region.Source & Drain are grounded and a positive voltage (vGS)is applied to the gate.An n channel is induced at the top of the substrate beneath the gate. In fact the path between Source & Drain (1012Ω) has very high resistanceįigure 4.2 The enhancement-type NMOS transistor with a positive voltage applied to the gate. No current flows even if vDSis applied.With no bias gate voltage, two back-to-back diodes exist in series between drain and source.It is a symmetrical device thus Drain & Source can be interchanged with no change in devices characteristics.Voltage applied to the Gate controls current flow between Source & Drain with direction from Drain to Source in channel region.

Thus Body will have no effect on operation of the device.

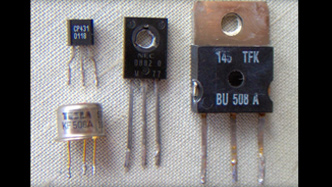

Implement digital & analog functions with a fewer resistors very large scale Integrated (VLSI) circuit įigure 4.1 Physical structure of the enhancement-type NMOS transistor:.NMOSFET/PMOSFET n/p-channel enhancement mode MOSFET.

1930 was Known, 1960s Commercialized 1970s Most commonly used VLSI.Uni-polar Current is conducted by only one carrier.FET Field Effect Transistor The current controlled mechanism is based on an electric field established by the voltage applied to the control terminal – GATE.MOS Metal Oxide Semiconductor Physical Structure.MOSFET ( Voltage Controlled Current Device)

0 kommentar(er)

0 kommentar(er)